### Enabling Low-Overhead and Scalable Near-Data Pattern Matching Acceleration with Memory-Centric Architectures

A Dissertation

Presented to the Faculty of the School of Engineering and Applied Science University of Virginia

> In Partial Fulfillment of the requirements for the Degree Doctor of Philosophy (Computer Engineering)

> > by

Reza Rahimi

December 2020

$\bigodot$  2020 Reza Rahimi

## Abstract

The growing need for accelerated pattern recognition and inexact pattern matching has motivated many efforts to design finite-automata-based, in-memory pattern-processing accelerators. However, the lack of a standard, scalable, open-source, and easy-to-modify framework has made it difficult to develop new applications and explore new architectural innovations. Moreover, none of the existing in-memory accelerators is designed to process multiple symbols at once. In addition, none has a reliable, efficient, and scalable reporting architecture to gather and analyze the reporting data.

This proposal outlines four novel software and hardware contributions to improve the effectiveness of pattern processing on big-data applications with real-time processing needs. (1) We propose a robust, easy-to-use/modify automata processing simulation, transformation, optimization, and performance modeling framework to facilitate automata application development and architectural explorations/innovations. (2) Motivated by our application analysis enabled by our framework, we observe a significant resource underutilization in the existing memory-based accelerators. We leverage this observation and propose an area-efficient, high-throughput, and energy-efficient in-SRAM architecture for multi-symbol pattern processing. (3) Inspired by our study on multi-symbol pattern matching in in-memory architectures, we explore temporal multi-symbol matching on FPGA platforms. Our framework enables us to process different bitwidths, which has shown to be beneficial for mapping different applications to platforms with different architectural parameters. (4) Finally, we analyze the reporting architecture of the existing state-of-the-art memory-centric solutions, and we find that these reporting architectures are either the major source of the area/performance inefficiency, or they are not scalable and general solutions. To address these issues, we propose a compact, reconfigurable, and easy-to-handle in-situ reporting architecture by re-purposing SRAM subarrays with negligible hardware overhead.

#### **Approval Sheet**

This dissertation is submitted in partial fulfillment of the requirements for the degree of Doctor of Philosophy (Computer Engineering)

Reza Rahimi

This dissertation has been read and approved by the Examining Committee:

Kevin Skadron , Adviser

Joanne Bechta Dugan

Mircea Stan

Brad Campbell

Ashish Venkat

Accepted for the School of Engineering and Applied Science:

Craig Benson, Dean, School of Engineering and Applied Science

December 2020

#### DEDICATION

I dedicate this dissertation to my wife, Elaheh, who has been a constant source of support, happiness, and encouragement during the challenges of my life from the first day I met her. I have learned living with passion from you and I am truly thankful for having you in my life.

# Acknowledgements

I am grateful to numerous people who have contributed towards shaping this dissertation. I could not have reached the finish line without the influence, advice, and support of many colleagues, friends, and family.

First, I would like to thank my advisor, Prof. Kevin Skadron, who has been a supportive mentor for me and has shaped my life in many profound ways. He always trusted in me and gave me tremendous freedom in pursuing my ideas, and this has made me an independent researcher. At the same time, he continued to contribute valuable feedback and encouragement. I will forever treasure the advice I have received from him.

I also wish to thank the members of my Ph.D. committee; Prof. Mircea Stan, Prof. Ashish Venkat, Prof. Joanne Dugan, and Prof. Brad Campbell for their many insightful discussions and suggestions on my research. I am grateful for having so many friends and collaborators both inside and outside of the Computer Engineering Department. To Tommy Tracy, Jack Wadden, Marzieh Lenjani, Viabhav Verma, Sergui Mosanu, Chunkun Bo, Oluwole Jaiyeoba, and Alif Ahmed; thank you for your help and support. Last but not least, I am deeply thankful to my family, for their unconditional love, support, and sacrifices.

Chapter 3 describes the framework that has enabled several papers [1, 2, 3, 4, 5]. The dissertation author was the primary investigator of this framework.

Chapter 4, in full, is a reprint of the material as it appears in proceeding of FCCM 2020 [2]. Rahimi, Reza; Sadredini, Elaheh; Stan, Mircea; Skadron, Kevin, "Grapefruit: An Open-Source, Full-Stack, and Customizable Automata Processing on FPGAs", The 28th IEEE International Symposium on Field-Programmable Custom Computing Machines (FCCM), 2020, **Best paper nominee.** The dissertation author is the primary investigator and author of this paper.

Chapter 5, in full, is a reprint of the material as it appears in proceeding of HPCA 2020 [1]. Rahimi, Reza; Sadredini, Elaheh; Lenjani, Marzieh; Stan, Mircea; Skadron, Kevin, "Impala: Algorithm/Architecture Co-Design for In-Memory Multi-Stride Pattern Matching", The 26th IEEE International Symposium on High-Performance Computer Architecture (HPCA), 2020. **Best paper nominee.** The dissertation author is the primary investigator and author of this paper. Chapter 6, partially, is a preprint of the material as it appears in Computer Architecture Letters, 2020. Rahimi, reza; Sadredini, Elaheh; Skadron, Kevin, "Enabling In-SRAM Pattern Processing with Low-Overhead Reporting Architecture", Computer Architecture Letters, 2020.

The longer version is currently under review. Rahimi, Reza; Sadredini, Elaheh; Skadron, Kevin, "Sunder: Enabling Low-Overhead and Scalable Near-Data Pattern Matching Acceleration." The dissertation author is the primary investigator and author of these papers.

The dissertation author is the secondary investigator and author of following related papers.

- Sadredini, Elaheh; Rahimi, Reza; Lenjani, Marziyeh; Stan, Mircea; Skadron, Kevin, "FlexAmata: A Universal and Efficient Adaption of Applications to Spatial Automata Processing Accelerators", The 25th International Conference on Architectural Support for Programming Languages and Operating Systems (ASPLOS), 2020.

- Sadredini, Elaheh; Rahimi, Reza; Verma, Vaibhav; Stan, Mircea; Skadron, Kevin, "A Scalable and Efficient in-Memory Interconnect Architecture for Automata Processing", Computer Architecture Letters (CAL), 2019.

- Sadredini, Elaheh; Rahimi, Reza; Verma, Vaibhav; Stan, Mircea; Skadron, Kevin, "eAP: A Scalable and Efficient in-Memory Accelerator for Automata Processing", 52th Annual IEEE/ACM International Symposium on Microarchitecture (MICRO'52), 2019.

- Angstadt, Kevin; Subramaniyan, Arun; Sadredini, Elaheh; Rahimi, Reza; Skadron, Kevin; Weimer, Westley; Das, Reetu, "ASPEN: A Scalable In-SRAM Architecture for Pushdown Automata", 51th Annual IEEE/ACM International Symposium on Microarchitecture (MICRO'51), 2018.

- Sadredini, Elaheh; Guo, Deyuan; Bo, Chunkun; Rahimi, Reza; Skadron, Kevin; Wang, Hongning, "A Scalable Solution for Rule-Based Part-of-Speech Tagging on Novel Hardware Accelerators", 24th ACMSIGKDD International Conference on Knowledge Discovery and Data Mining (KDD), 2018.

- Sadredini, Elaheh; Rahimi, Reza; Wang, Ke; Skadron, Kevin, "Frequent Subtree Mining on the Automata Processor: Opportunities and Challenges", International Conference on Supercomputing (ICS), 2017.

This dissertation is funded, in part, by the NSF (CCF-1629450) and CRISP, one of six centers in JUMP, a Semiconductor Research Corporation (SRC) program sponsored by MARCO and DARPA.

# Contents

| $\mathbf{C}$ | ontei             | nts                                                                                                                | vi              |

|--------------|-------------------|--------------------------------------------------------------------------------------------------------------------|-----------------|

|              | List              | of Tables                                                                                                          | ix              |

|              | List              | of Figures                                                                                                         | х               |

| 1            | Inti              | roduction                                                                                                          | 1               |

| -            | 1.1               | Contributions                                                                                                      | 4               |

|              | 1.1               | 1.1.1       APSim: Automata Simulation and Transformation                                                          | 4               |

|              |                   | 1.1.1       Ar Shill, Automata Shilulation and Transformation         1.1.2       Multi-Symbol Processing on FPGAs | $\frac{4}{5}$   |

|              |                   | · · · · · ·                                                                                                        | 5<br>5          |

|              |                   | 1.1.3 Algorithm/Architecture Methodology for In-Memory Multi-Stride Pattern Matching                               | Э               |

|              |                   | 1.1.4 Enabling Low-Overhead Reporting Architecture in Memory-Centric Pattern Matching                              | 0               |

|              |                   | Accelerators                                                                                                       | 6               |

|              |                   | 1.1.5 Summary                                                                                                      | 7               |

|              | 1.2               | Overview of Dissertation                                                                                           | 7               |

| 2            | Bac               | ckground                                                                                                           | 9               |

|              | 2.1               | Finite Automata                                                                                                    | 9               |

|              | 2.2               | Automata Processing on von Neumann Architectures                                                                   | 9               |

|              | 2.3               | Automata Processing on Memory-Centric Architectures                                                                | 10              |

|              |                   | 2.3.1 Automata Processor                                                                                           | 10              |

|              |                   | 2.3.2 Cache Automaton                                                                                              | 11              |

|              |                   | 2.3.3 Working Example on In-Memory Automata Accelerators                                                           | $12^{11}$       |

|              | 2.4               | Automata Processing on FPGAs                                                                                       | 13              |

|              | $2.4 \\ 2.5$      | Automata Processing on ASIC                                                                                        | 14              |

|              |                   |                                                                                                                    |                 |

| 3            |                   | tomata Simulation and Transformation                                                                               | 15              |

|              | 3.1               | Motivation: The Need for Automata Simulator                                                                        | 15              |

|              | 3.2               | APSim - A Cycle Accurate Automata Simulator: Current and Proposed Contributions                                    | 17              |

|              | 3.3               | Automata Transformation                                                                                            | 18              |

|              |                   | 3.3.1 Transformation Methodology                                                                                   | 19              |

|              |                   | 3.3.2 Transformation Soundness                                                                                     | 20              |

|              |                   | 3.3.3 Time Complexity                                                                                              | 21              |

|              |                   | 3.3.4 Non-divisible bitwidths effect                                                                               | 22              |

|              | 3.4               | APSim Contribution to the Research                                                                                 | 22              |

| 4            | On                | en-Source, Full-Stack, and Customizable Automata Processing Engine on FPGAs                                        | 23              |

| 4            | 4.1               | Background                                                                                                         | <b>23</b><br>25 |

|              | 4.1               | Related Work                                                                                                       | $\frac{20}{26}$ |

|              | $\frac{4.2}{4.3}$ | Grapefruit Framework                                                                                               | $\frac{20}{28}$ |

|              | 4.0               |                                                                                                                    | $\frac{28}{28}$ |

|              |                   |                                                                                                                    | 28<br>33        |

|              | 4 4               | 4.3.2 Compiler Optimizations                                                                                       |                 |

|              | 4.4               | Evaluation Methodology                                                                                             | 35<br>26        |

|              | 4.5               | Experimental Results                                                                                               | 36              |

|              |                   | 4.5.1 LUT-based vs. DRAM-based design                                                                              | 36              |

|   | 4.6                                           | .5.3 Comparison with prior work                                                                                                                                                                          | 38<br>38<br>39                                                                                                                                                                     |

|---|-----------------------------------------------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

| 5 | Alg                                           | ithm/Architecture Co-Design for In-Memory Multi-Stride Pattern Matching                                                                                                                                  | 40                                                                                                                                                                                 |

| 0 | 5.1                                           |                                                                                                                                                                                                          | <b>4</b> 2                                                                                                                                                                         |

|   | 5.2                                           |                                                                                                                                                                                                          | 44                                                                                                                                                                                 |

|   | 0.2                                           |                                                                                                                                                                                                          | 44                                                                                                                                                                                 |

|   |                                               |                                                                                                                                                                                                          | 45                                                                                                                                                                                 |

|   | 5.3                                           |                                                                                                                                                                                                          | 49                                                                                                                                                                                 |

|   | 0.0                                           |                                                                                                                                                                                                          | 49                                                                                                                                                                                 |

|   |                                               | •                                                                                                                                                                                                        | 49<br>51                                                                                                                                                                           |

|   | 5.4                                           |                                                                                                                                                                                                          | $51 \\ 55$                                                                                                                                                                         |

|   | $5.4 \\ 5.5$                                  | v 0                                                                                                                                                                                                      | 55                                                                                                                                                                                 |

|   | 5.6                                           |                                                                                                                                                                                                          | 50                                                                                                                                                                                 |

|   | 5.0                                           | ±                                                                                                                                                                                                        | 57<br>57                                                                                                                                                                           |

|   |                                               | •                                                                                                                                                                                                        | 57<br>59                                                                                                                                                                           |

|   |                                               |                                                                                                                                                                                                          |                                                                                                                                                                                    |

|   |                                               |                                                                                                                                                                                                          | 60                                                                                                                                                                                 |

|   |                                               |                                                                                                                                                                                                          | 61                                                                                                                                                                                 |

|   |                                               |                                                                                                                                                                                                          | 61                                                                                                                                                                                 |

|   |                                               | 1                                                                                                                                                                                                        | 62                                                                                                                                                                                 |

|   | 5.7                                           | Conclusions                                                                                                                                                                                              | 63                                                                                                                                                                                 |

| 6 | Eng                                           | ing Low-Overhead and Scalable Near-Data Pattern Matching Acceleration                                                                                                                                    | 64                                                                                                                                                                                 |

| U | 6.1                                           |                                                                                                                                                                                                          | 66                                                                                                                                                                                 |

|   | 0.1                                           | 8                                                                                                                                                                                                        | 66                                                                                                                                                                                 |

|   | 6.2                                           |                                                                                                                                                                                                          | 67                                                                                                                                                                                 |

|   | 0.2                                           |                                                                                                                                                                                                          | 68                                                                                                                                                                                 |

|   | 6.3                                           |                                                                                                                                                                                                          | 69                                                                                                                                                                                 |

|   | 6.4                                           |                                                                                                                                                                                                          |                                                                                                                                                                                    |

|   | 0.4                                           |                                                                                                                                                                                                          | 71                                                                                                                                                                                 |

|   |                                               | 1.1 Transforming to Nibble Processing                                                                                                                                                                    | 71<br>72                                                                                                                                                                           |

|   |                                               |                                                                                                                                                                                                          | 72                                                                                                                                                                                 |

|   | C E                                           | .4.2 Temporal Striding                                                                                                                                                                                   | 72<br>73                                                                                                                                                                           |

|   | 6.5                                           | .4.2 Temporal Striding                                                                                                                                                                                   | 72<br>73<br>73                                                                                                                                                                     |

|   | 6.5                                           | .4.2 Temporal Striding                                                                                                                                                                                   | 72<br>73<br>73<br>73                                                                                                                                                               |

|   | 6.5                                           | .4.2 Temporal Striding                                                                                                                                                                                   | 72<br>73<br>73<br>73<br>73<br>77                                                                                                                                                   |

|   |                                               | .4.2 Temporal Striding                                                                                                                                                                                   | 72<br>73<br>73<br>73<br>73<br>77<br>79                                                                                                                                             |

|   | 6.6                                           | .4.2 Temporal Striding                                                                                                                                                                                   | 72<br>73<br>73<br>73<br>77<br>79<br>80                                                                                                                                             |

|   | 6.6<br>6.7                                    | .4.2 Temporal Striding         under Architecture         .5.1 State Matching         .5.2 Reporting Architecture         .5.3 Interconnect         .5.3 Interconnect         .5.4 Waluation Methodology | 72<br>73<br>73<br>73<br>77<br>79<br>80<br>81                                                                                                                                       |

|   | 6.6                                           | .4.2 Temporal Striding                                                                                                                                                                                   | 72<br>73<br>73<br>73<br>77<br>79<br>80<br>81<br>82                                                                                                                                 |

|   | 6.6<br>6.7                                    | .4.2 Temporal Striding                                                                                                                                                                                   | <ol> <li>72</li> <li>73</li> <li>73</li> <li>73</li> <li>77</li> <li>79</li> <li>80</li> <li>81</li> <li>82</li> <li>82</li> <li>82</li> </ol>                                     |

|   | 6.6<br>6.7                                    | 4.2 Temporal Striding                                                                                                                                                                                    | <ol> <li>72</li> <li>73</li> <li>73</li> <li>73</li> <li>77</li> <li>79</li> <li>80</li> <li>81</li> <li>82</li> <li>82</li> <li>83</li> </ol>                                     |

|   | 6.6<br>6.7                                    | 4.2 Temporal Striding                                                                                                                                                                                    | 72<br>73<br>73<br>73<br>73<br>77<br>79<br>80<br>81<br>82<br>82<br>83<br>85                                                                                                         |

|   | 6.6<br>6.7<br>6.8                             | 4.2 Temporal Striding                                                                                                                                                                                    | 72<br>73<br>73<br>73<br>77<br>79<br>80<br>81<br>82<br>82<br>83<br>85<br>85                                                                                                         |

|   | 6.6<br>6.7                                    | 4.2 Temporal Striding                                                                                                                                                                                    | 72<br>73<br>73<br>73<br>73<br>77<br>79<br>80<br>81<br>82<br>82<br>83<br>85                                                                                                         |

| 7 | 6.6<br>6.7<br>6.8<br>6.9                      | 4.2 Temporal Striding                                                                                                                                                                                    | 72<br>73<br>73<br>73<br>77<br>79<br>80<br>81<br>82<br>83<br>85<br>85<br>87<br>88                                                                                                   |

| 7 | 6.6<br>6.7<br>6.8<br>6.9<br><b>Cor</b>        | 4.2 Temporal Striding                                                                                                                                                                                    | 72<br>73<br>73<br>73<br>77<br>79<br>80<br>81<br>82<br>83<br>85<br>85<br>87<br>88<br><b>89</b>                                                                                      |

| 7 | 6.6<br>6.7<br>6.8<br>6.9<br><b>Cor</b><br>7.1 | 4.2 Temporal Striding                                                                                                                                                                                    | <ol> <li>72</li> <li>73</li> <li>73</li> <li>77</li> <li>79</li> <li>80</li> <li>81</li> <li>82</li> <li>83</li> <li>85</li> <li>87</li> <li>88</li> <li>89</li> <li>89</li> </ol> |

| 7 | 6.6<br>6.7<br>6.8<br>6.9<br><b>Cor</b>        | 4.2 Temporal Striding                                                                                                                                                                                    | 72<br>73<br>73<br>73<br>77<br>79<br>80<br>81<br>82<br>83<br>85<br>83<br>85<br>85<br>88<br>89<br>91                                                                                 |

| 7 | 6.6<br>6.7<br>6.8<br>6.9<br><b>Cor</b><br>7.1 | 4.2 Temporal Striding                                                                                                                                                                                    | 72<br>73<br>73<br>73<br>77<br>79<br>80<br>81<br>82<br>83<br>85<br>83<br>85<br>87<br>88<br>89<br>91<br>91                                                                           |

| 7 | 6.6<br>6.7<br>6.8<br>6.9<br><b>Cor</b><br>7.1 | 4.2 Temporal Striding                                                                                                                                                                                    | 72<br>73<br>73<br>73<br>77<br>79<br>80<br>81<br>82<br>83<br>85<br>83<br>85<br>88<br>89<br>91<br>91<br>92                                                                           |

| 7 | 6.6<br>6.7<br>6.8<br>6.9<br><b>Cor</b><br>7.1 | 4.2 Temporal Striding                                                                                                                                                                                    | 72<br>73<br>73<br>73<br>77<br>79<br>80<br>81<br>82<br>83<br>85<br>83<br>85<br>87<br>88<br>89<br>91<br>91<br>92<br>92                                                               |

| 7 | 6.6<br>6.7<br>6.8<br>6.9<br><b>Cor</b><br>7.1 | 4.2 Temporal Striding                                                                                                                                                                                    | 72<br>73<br>73<br>73<br>77<br>79<br>80<br>81<br>82<br>83<br>85<br>83<br>85<br>87<br>88<br>89<br>91<br>91<br>92<br>92<br>92                                                         |

| 7 | 6.6<br>6.7<br>6.8<br>6.9<br><b>Cor</b><br>7.1 | 4.2 Temporal Striding                                                                                                                                                                                    | 72<br>73<br>73<br>73<br>77<br>79<br>80<br>81<br>82<br>83<br>85<br>83<br>85<br>87<br>88<br>89<br>91<br>91<br>92<br>92                                                               |

#### Bibliography

# List of Tables

| $4.1 \\ 4.2$ | Benchmark Overview                                                                                                                                                                                                                                                                                                                                                                                         | 36              |

|--------------|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

| 4.2          | processing).                                                                                                                                                                                                                                                                                                                                                                                               | 37              |

| 4.3          | Striding and signal-sharing effect for TCP benchmark.                                                                                                                                                                                                                                                                                                                                                      | $\frac{37}{37}$ |

| 5.1          | Relative compilation time across architectures.                                                                                                                                                                                                                                                                                                                                                            | 48              |

| 5.2          | Benchmark Overview                                                                                                                                                                                                                                                                                                                                                                                         | 56              |

| 5.3          | Subarray parameters for state-matching and interconnect (overhead of peripherals are included).                                                                                                                                                                                                                                                                                                            | 57              |

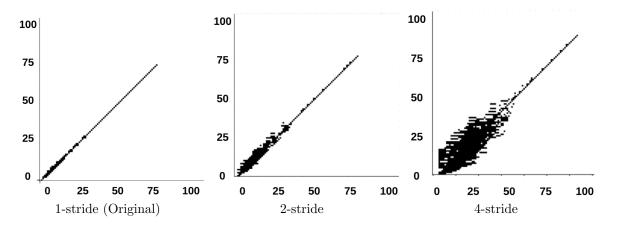

| 5.4          | States and transitions overhead in different strides for V-TeSS normalized to the original 8-bit design. For example, 2-stride processes $4\times 2$ bits of input in each cycle and has $1.12\times$ more states and $1.34\times$ more transitions than the original 8-bit design. However, 4-bit design needs memory columns with $2^4$ rows while 8-bit design requires memory columns with $2^8$ rows. | 58              |

| 5.5          | Pipeline stage delays and operating frequency. The detail implementation of the AP is not                                                                                                                                                                                                                                                                                                                  | 59              |

| 5.6          | publicly available.                                                                                                                                                                                                                                                                                                                                                                                        | $\frac{59}{62}$ |

| 6.1          | Reporting behavior summary                                                                                                                                                                                                                                                                                                                                                                                 | 70              |

| 6.2          | Subarray parameters for state-matching and interconnect (overhead of peripherals are included)                                                                                                                                                                                                                                                                                                             |                 |

|              | in 14nm technology.                                                                                                                                                                                                                                                                                                                                                                                        | 81              |

| 6.3          | Number of state and transitions in Sunder normalized to the original 8-bit automata                                                                                                                                                                                                                                                                                                                        | 83              |

| 6.4          | Number of state and transitions in Sunder normalized to the original 8-bit automata                                                                                                                                                                                                                                                                                                                        | 84              |

| 6.5          | Reporting overhead for four nibble processing.                                                                                                                                                                                                                                                                                                                                                             | 85              |

| 6.6          | Pipeline stage delays and operating frequency. The detail implementation of the AP is not                                                                                                                                                                                                                                                                                                                  |                 |

|              | publicly available.                                                                                                                                                                                                                                                                                                                                                                                        | 86              |

# List of Figures

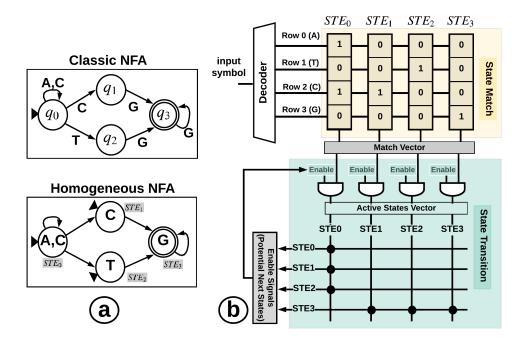

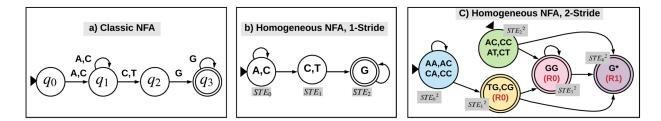

| 2.1                                       | (a) Different NFA representation, (b) A simplified in-memory automata processing model $\ .$ .                                                                                                                                                                           | 13              |

|-------------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------|

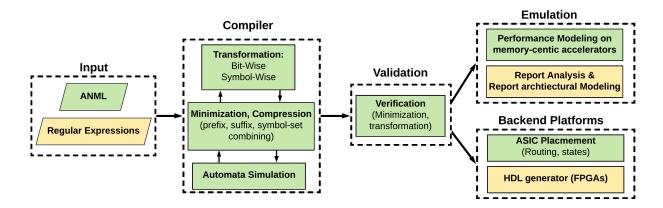

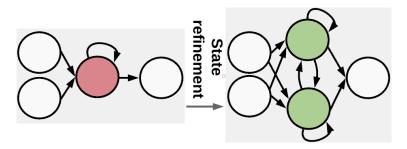

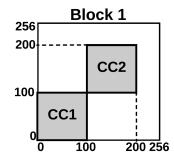

| $3.1 \\ 3.2$                              | APSim Components                                                                                                                                                                                                                                                         | 18              |

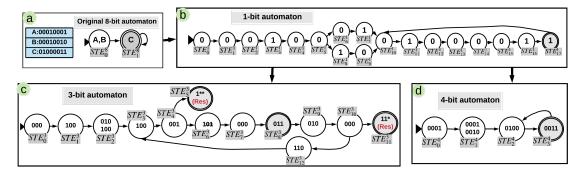

| 9.9                                       | 4-bit (d) automata are generated from the 1-bit automaton.                                                                                                                                                                                                               | 20              |

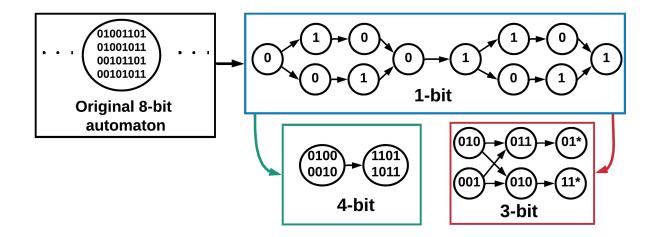

| 3.3                                       | State and transition overhead is less in divisible bitwidths (4-bit) than non-divisible bitwidths (3-bit)                                                                                                                                                                | 22              |

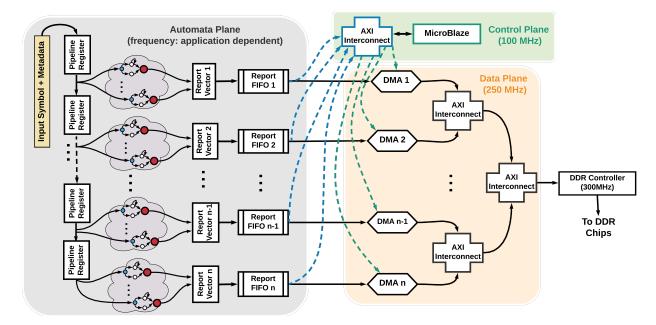

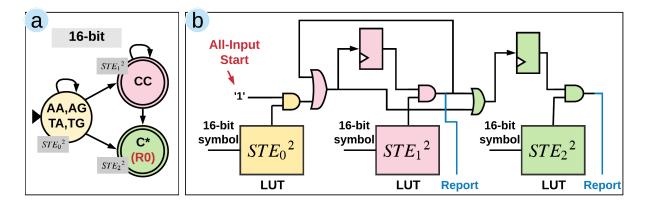

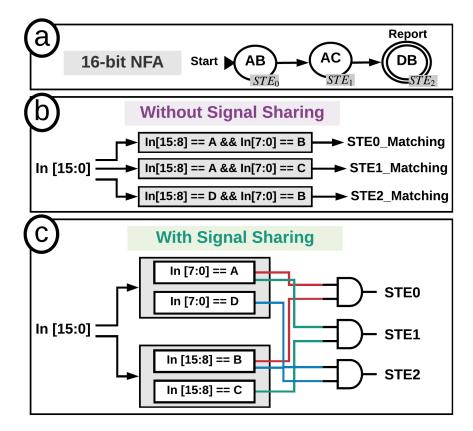

| $\begin{array}{c} 4.1 \\ 4.2 \end{array}$ | (a) Classic NFA, (b) Homogeneous NFA, (c) Equivalent 2-stride automata Automata processing architecture on FPGAs. The cloud-shaped entities show several connected                                                                                                       | 25              |

| 4.3                                       | components.       Automata mapping in LUT-based design.         Automata mapping in DDAM based design.                                                                                                                                                                   | 27<br>30        |

| $4.4 \\ 4.5$                              | Automaton mapping in BRAM-based design.         An example on signal sharing.                                                                                                                                                                                            | 31<br>33        |

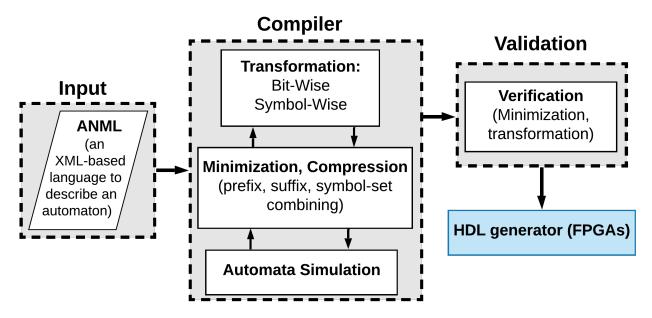

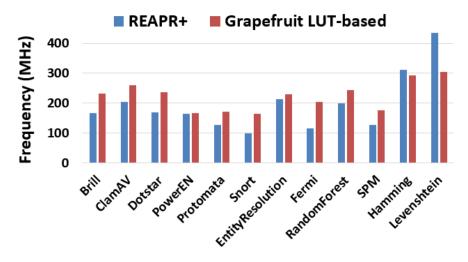

| $\begin{array}{c} 4.6 \\ 4.7 \end{array}$ | Different components in our back-end compiler                                                                                                                                                                                                                            | $\frac{34}{38}$ |

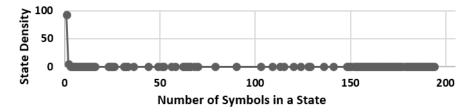

| 5.1                                       | Normalized histogram of the states based on the number of accepting symbols. More than $86\%$ of the states accept less than 8 symbols. More than $73\%$ of the states only accept one symbol.                                                                           | 44              |

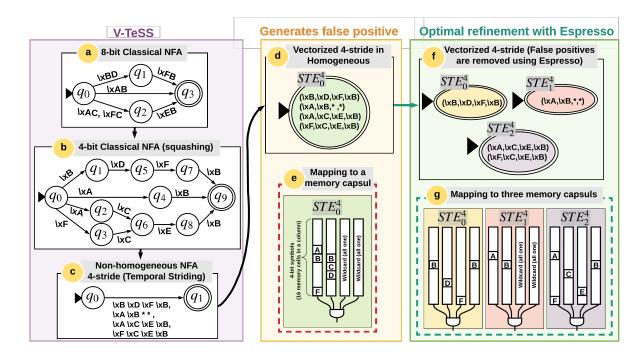

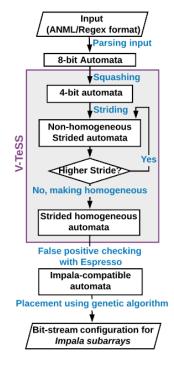

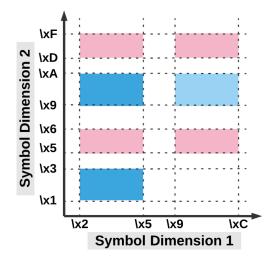

| 5.2                                       | (a) Original 8-bit automaton. (b) Squashing the automaton in (a) to 4-bit processing. (c) Striding 4-bit automaton in (b) to process 16 bits/cycle. (d) Converting the automaton in (c)                                                                                  |                 |

|                                           | to its homogeneous representation. (e) Mapping $STE_0^4$ in (d) to one, which produces false positive reports (e.g., $(\xB, \xD, \xE, \xB)$ generates a false report). (f) Espresso solves it with minimal state splitting. (g) The states in (f) are mapped to three s. | 46              |

| 5.3                                       | Offline pre-processing steps to prepare bit-streams to be configured on Impala's memory                                                                                                                                                                                  | 40              |

| 5.4                                       | subarrays                                                                                                                                                                                                                                                                | 48              |

|                                           | automaton.                                                                                                                                                                                                                                                               | 49              |

| 5.5<br>5.6                                | An example of an STE matching regions in a 2-stride automaton                                                                                                                                                                                                            | $\frac{50}{51}$ |

| 5.7                                       | Full-crossbar resource utilization.                                                                                                                                                                                                                                      | 52              |

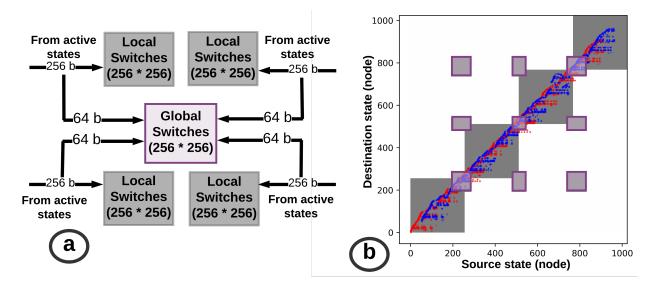

| 5.8                                       | Union heatmap of routing switches with BFS labeling for all the connected components in Dotstar06. States are labeled with BFS starting from the start states. Each dark point at                                                                                        | 59              |

| 5.9                                       | (x,y) shows an edge from state $y$ to state $x$                                                                                                                                                                                                                          | $53 \\ 54$      |

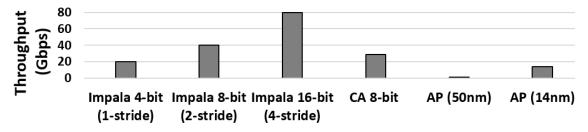

|                                           | Overall performance of different spatial automata accelerators in Gbps.                                                                                                                                                                                                  | 60              |

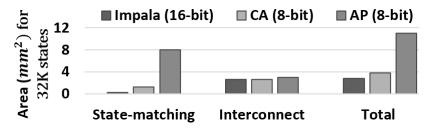

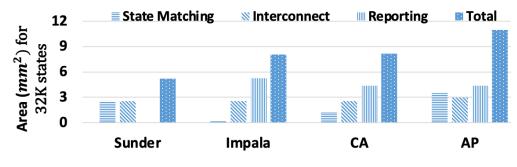

|                                           | Comparing area overhead for 32K STEs                                                                                                                                                                                                                                     | 60              |

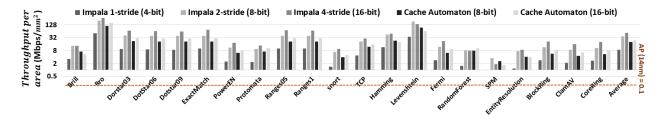

| 5.12                                      | Comparing throughput per $mm^2$ area among Impala 4-bit design in different strides, Cache Automata (original 8bit design) in 1-stride and 2-stride, and the Automata Processor (AP),                                                                                    |                 |

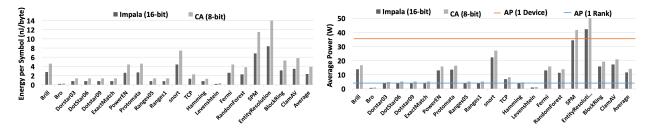

| 5 1 3                                     | all in 14nm                                                                                                                                                                                                                                                              | 61              |

| 5.10                                      | of Impala compared to CA and the AP (reported by Micron [7]).                                                                                                                                                                                                            | 61              |

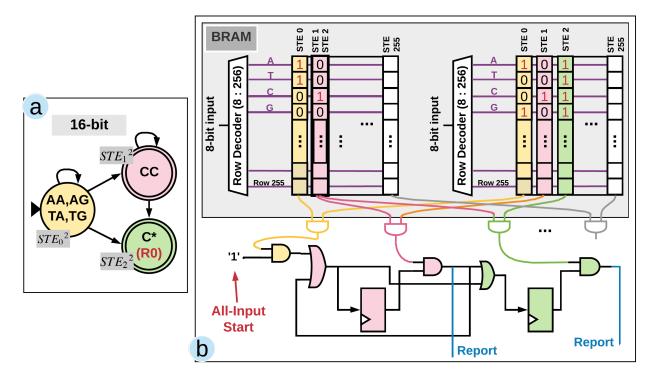

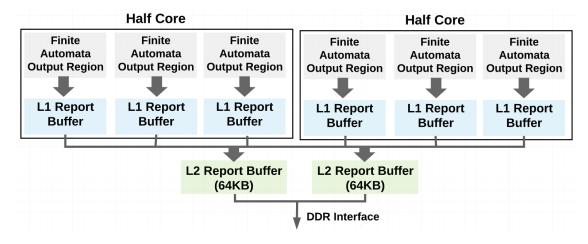

| 6.1 | The Automata Processor reporting architecture.                                                | 67 |

|-----|-----------------------------------------------------------------------------------------------|----|

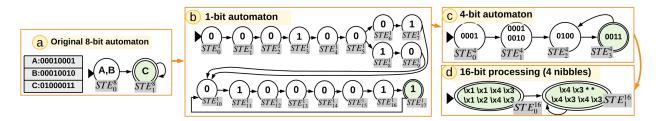

| 6.2 | An 8-bit automaton (a) is converted to the minimized 1-bit automaton (b). The 4-bit automaton |    |

|     | (c) is generated from the 1-bit automaton. Finally, the 4-bit automaton (C) is strided to a   |    |

|     | 16-bit processing (d) using nibble units.                                                     | 72 |

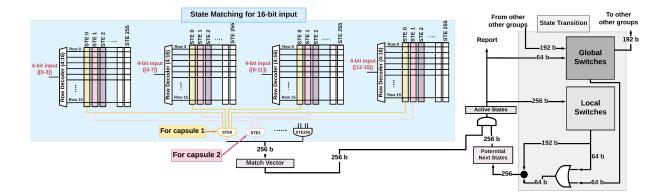

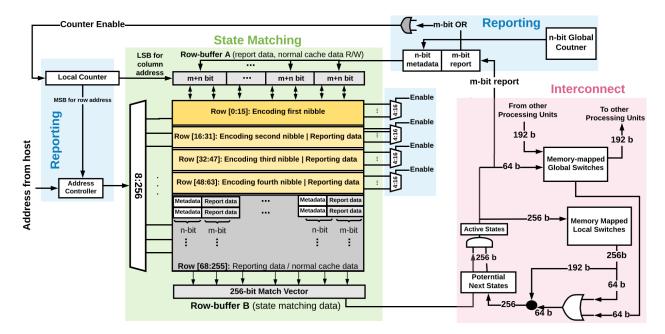

| 6.3 | Sunder architecture for state matching (green), state transition or interconnect (pink), and  |    |

|     | reporting (blue). The state matching subarray is repurposed for storing reporting data in     |    |

|     | addition to storing matching data.                                                            | 74 |

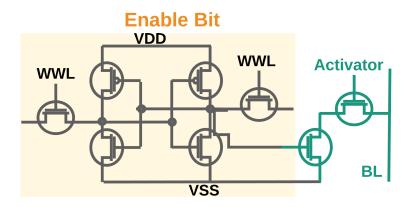

| 6.4 | 8T SRAM cell                                                                                  | 76 |

| 6.5 | Memory-mapped local & global interconnect                                                     | 80 |

| 6.6 | Throughput of different spatial automata accelerators.                                        | 86 |

| 6.7 | Comparing area overhead for 32K STEs                                                          | 87 |

| 6.8 | Performance slowdown for various reporting rates.                                             | 87 |

List of Figures

### Chapter 1

# Introduction

In today's big data era, and with the rise of AI, mobile, and IoT applications, processing and analyzing large data sets drives the demand for more computation and puts even larger demand on the memory and storage infrastructure. The problem is more challenging when a real-time analysis is critical (e.g., in edge devices). However, classic Moore's Law is slowing down, Dennard scaling has stopped; the amount of computation per unit cost and power is no longer increasing at its historic rate. At the same time, the performance gap between processing units and memory is increasing (also known as the *memory wall* [8]), and this is a major source of performance bottleneck for memory-bound, data-intensive applications. A further source of inefficiency is that the raw bandwidth at the edge of data arrays is 1-2 orders of magnitude greater than what can be transmitted off-chip. Therefore, many of the questions we want to explore with growing data remain unanswerable because we lack the computational power to analyze these huge data sets in a timely and cost-effective fashion.

Solving these challenges and enabling the next-generation of data-intensive applications requires computing to be embedded near the data. A recent trend in accelerator design is combining processing logic with memory elements, aka *processing-in-memory (PIM)*, to perform computation as close to where the data are located as possible, in order to exploit massive bandwidth and scalable parallelism [9, 10, 11, 12, 13, 14, 15, 16, 17, 18, 19, 20, 21, 22]. This extracts the full compute and storage power from the underlying hardware and allows superior performance and energy-efficiency, especially for memory-bound big-data applications by removing the data movement cost.

Complex and inexact pattern matching kernels in big-data domains, where millions of patterns should be processed at once, are extremely memory-bound [23, 24, 25, 26, 27, 28, 29, 30]. High-throughput and concurrent processing of thousands of patterns on each byte of an input stream is critical for many applications with real-time and high-throughput processing requirements, such as network intrusion detection, spam filters, virus scanners, and many more. One prominent way of processing patterns is to use regular expressions. They are used in identifying complex patterns and variants of base patterns, potentially the most time-consuming task in many big-data applications.

Regular expressions are a widely used pattern specification language, and they are efficiently implemented via Finite Automata (a form of finite state machines) [31], with important applications in network security [32, 33, 34, 35, 36], log analysis [37], and many more. There are many other applications in domains such as data-mining [27, 24, 38, 25], bioinformatics [39, 23], machine learning [40, 41], natural language processing [26, 29], big data analytics [42], and even particle physics [43], that shown to greatly benefit from accelerated automata processing. The automata structure in these applications differ significantly in static structure and dynamic behavior from existing regular expression benchmarks [44, 45]. These properties, combined with increasing data being collected in big-data domain and time-sensitive applications, make pattern matching even more challenging for these applications.

A regular expression can be represented by either deterministic finite automata (DFA) or non-deterministic finite automata (NFA), which are equivalent in computational power. On CPUs, NFAs and DFAs are represented by tables indicating each state's successor state(s) upon a rule match. DFAs are often the basis for implementing automata on CPUs, because they have predictable memory bandwidth requirements (one lookup per input); while an NFA may have many active states and may require many state lookups to process a single input symbol (potentially leading to a very large memory bandwidth requirement), a DFA requires just one. On the other hand, DFA tables are often too large to fit in the processor caches, because DFAs often suffer an exponential increase in the number of states relative to NFAs [46] (See Chapter 2 for more detail).

Graphics processing units (GPUs) provide a large number of parallel resources, which can help in hiding the DRAM access latency. However, highly-random access patterns in automata processing exhibit poor memory locality and increase branch divergence and need for synchronization [44, 47, 48, 49]. Despite its foundation's importance, the efficient implementation of finite automata processing remains a challenging open research problem and the subject of extensive research.

Researchers are increasingly exploiting memory-centric hardware accelerators to meet demanding real-time requirements as performance growth in conventional processors is slowing down. The growing demand for accelerated automata processing has motivated many efforts in designing regular expression and general automata accelerators on ASIC [50, 37], FPGAs [51, 52, 36, 53, 54], and processing-in-memory (PIM) designs [55, 30, 56, 4, 57]. Spatial memory-centric accelerators, such as FPGAs and in-memory solutions, provide a reconfigurable substrate to lay out the rules in hardware by placing-and-routing automata states and connections onto a pool of hardware units in logic- or memory-based fabrics. This allows a large number of automata to be executed in parallel, up to the hardware capacity, in contrast to von Neumann architectures such as CPUs that must handle one rule at a time in each core. Moreover, real-world automata benchmarks are often extensive in terms of state count, too big to fit in a single hardware unit, and in current memory-centric architectures, usually need multiple rounds of reconfiguration and re-processing of the data. Therefore, design density plays a vital role in overall performance.

Automata processing research focuses mainly on two dimensions: (1) application development, where obvious applications (e.g., regular expressions) or non-obvious applications (e.g., frequent subtree mining [27], sequential pattern mining [24], part-of-speech tagging [26], entity resolution [42], genome sequencing [39], random forest [58], etc.) are mapped to automata computation and processed on automata processing hardware, and (2) architectural development [4, 55, 59]. Unfortunately, the available tools for both research areas are not comprehensive, parametrizable, and easy-to-modify. Different components are scattered among multiple tools, which make it even harder to explore new research ideas.

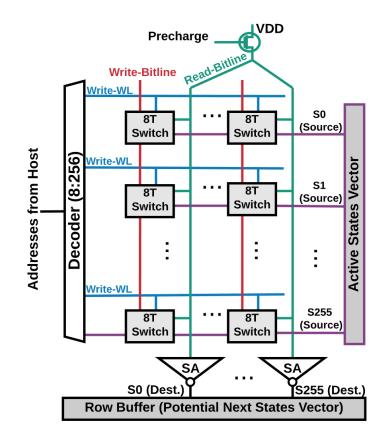

In-memory automata processing model has three processing stages, state-matching, state-transition, and report-gathering, and can be combined in a pipeline fashion. In the state-matching stage, the current input symbol is decoded and all the states whose symbols match against it are detected by reading a memory row. In the state-transition stage, successors of active states are determined by propagating signals via an interconnect. In the report-gathering phase, the report data is gathered and analyzed for the final action or decision.

In the existing in-memory automata accelerators, 50%-70% of hardware resources are spent for statematching [56, 60, 30, 4]. We study the state-matching resource utilization across a diverse set of automata benchmarks, and we found 86% of the time, only 3% of resources are utilized! This is mainly because in all these architectures, each state is modeled with a memory column of size 256, and 8-bit symbols are one-hot encoded in the memory columns to be able to accept a range of symbols (up to 256 symbols) in each state. However, the number of symbols accepted by a state is fewer than 8 symbols 86% of the time. This, in turn, implies that the classic approach of one-hot encoding for matching drastically over-provisions state-matching resources, which incurs significant performance penalties and leads to an inefficient and costly design. Our key observations are: (1) all these architectures are based on 8-bit symbol processing (derived from ASCII), and our analysis on a large set of real-world automata benchmarks reveals that the 8-bit processing dramatically underutilizes hardware resources for state-matching, and (2) multi-stride symbol processing, a major source of throughput growth, is not explored in the existing in-memory solutions.

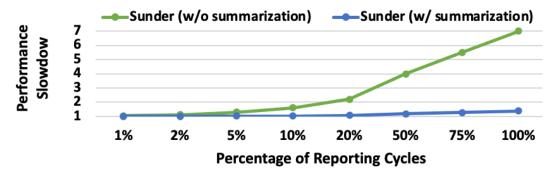

Moreover, prior work has either neglected the real cost of providing a reporting architecture [30, 1] or incur a significant cost when it is considered accurately. For example, the reporting architecture in the Automata Processor [61] has 40% area overhead and up to 46× performance overhead over the ideal case due to buffer flush overhead. Other reporting solutions [62] suffer from congested routing, frequent stalling, and lack of control on the hardware for efficient report analysis, and all these make the realistic in-memory pattern processing very inefficient and hard to scale-up.

#### 1.1 Contributions

In this dissertation, We hypothesize that efficient software/hardware methodology can enable performance, power, and area improvements in memory-centric pattern matching accelerators over CPU/GPU solutions, Cache Automaton, and Micron's Automata Processor. To evaluate this hypothesis, this dissertation proposes to address several previously unexplored problems in memory-centric automata accelerators by investigating the strength and limits of existing memory-centric automata processing accelerators, and (1) developing an automata processing framework to address the issues of existing tools and provide a flexible, powerful, and easy-to-use/modify structure to explore new research ideas, (2) investigating efficient algorithm/hardware design methodologies for automata processing model to support multi-symbol processing on FPGAs and in-memory solutions, which enables performance, power, and area efficiency, and (3) proposing an efficient, compact, and scalable in-situ reporting architecture to enable a realistic in memory-centric architecture for next generation pattern processing accelerators.

#### 1.1.1 APSim: Automata Simulation and Transformation

In this chapter, we present an open-source automata processing simulator and a compiler that simulates, minimizes, compresses, and transforms a set of automata to different symbol sizes, and efficiently maps them to the hardware resources in memory-centric architectures, such as FPGAs, Cache Automaton [30], eAP [4], etc. APSim provides a parameterizable environment to experiment with bitwidth sizes on various platforms. A set of bitwise and symbol-wise automata transformation and minimization algorithms are developed to enable these explorations.

APSim addresses the state and transition placement in an automaton by converting it to the subgraph isomorphism problem, and applies the genetic algorithm approach to map states/transitions to their physical locations. Moreover, unlike prior works, APSim uses a well-known and actively maintained python graph processing package as its main building block to benefit from its reliability, speed, and massive documentation with examples for further development by other collaborators.

#### 1.1.2 Multi-Symbol Processing on FPGAs

Processing multiple symbols per cycle (also known as symbol striding) in regular expression has been explored in several prior work [63, 64, 65, 36] in academia. However, currently, there is no such tool publicly available for automata processing to be used by an end-user for setting up an FPGA-based multi-symbol pattern matching system.

In this chapter, we present *Grapefruit* (General and Reconfigurable Automata ProcEssing FRamework Using Integrated Reporting and InTerconnect). We prioritize flexibility, extensibility, and scalability while developing this tool to provide an easy-to-understand interface and easy-to-modify code for other researchers to explore new features and design parameters.

Grapefruit integrates our multi-symbol processing solution on FPGA into our APSim framework to transform any given input automaton (which process one symbol per cycle) to a new automaton that processes multiple symbols per cycle where the number of symbols can be selected by the user. In addition, this tool will provide multiple FPGA design choices such as symbol-width conversion by FlexAmata [66], freedom in BRAM/LUT matching selection for every state in every symbol, BRAM matching sharing for states with the same matching condition on the same input symbol, and alphabet compression.

Our results confirm that we are achieving 9%-80% higher frequency in a single-stride solution than prior works that are not fully end-to-end (including reporting and I/O) and  $3.4\times$  higher throughput in a multi-stride solution than a single-stride solution.

### 1.1.3 Algorithm/Architecture Methodology for In-Memory Multi-Stride Pattern Matching

From studying prior architectures, we observed that: (1) all these architectures are based on 8-bit symbol processing (derived from ASCII), and our analysis on a large set of real-world automata benchmarks reveals that the 8-bit processing dramatically underutilizes hardware resources, and (2) multi-stride symbol processing, a major source of throughput growth, is not explored in the existing in-memory solutions.

This chapter presents Impala [1], a software/hardware design methodology for multi-stride in-memory automata processing by leveraging our observations. The key insight of our work is that transforming 8-bit processing to 4-bit processing exponentially reduces hardware resources for state-matching and improves resource utilization. This, in turn, brings the opportunity to have a denser design, and be able to utilize more memory columns to process multiple symbols per cycle with a linear increase in state-matching resources.

Impala proposes an in-SRAM solution and introduces three-fold area, throughput, and energy benefits at the expense of increased offline compilation time. These three-fold efficiencies are obtained from (1) an architectural contribution that utilizes *shorter-and-parallel* SRAM-subarrays instead of *longer-and-serial* subarrays, and (2) an algorithmic contribution which efficiently transforms an automaton and maps it to Impala's resources. To the best of our knowledge, this is the first work that observes state-matching inefficiency in memory-centric accelerators and proposes an algorithm/architecture co-design for *multi-stride* automata processing for in-situ computations.

Our empirical evaluations on a wide range of automata benchmarks reveal that Impala has on average  $2.7 \times$  (up to  $3.7 \times$ ) higher throughput per unit area and  $1.22 \times$  lower power consumption than Cache Automaton, which is the best performing prior work.

### 1.1.4 Enabling Low-Overhead Reporting Architecture in Memory-Centric Pattern Matching Accelerators

Prior memory-centric pattern matching solutions have either neglected the real cost of providing a reporting architecture [30, 1] or incur a significant cost when it is considered accurately. For example, the reporting architecture in the Automata Processor [61] has 40% area overhead and up to 46× performance overhead over the ideal case due to buffer flush overhead. Other reporting solutions [62] suffer from congested routing, frequent stalling, and lack of control on the hardware for efficient report analysis, and all these make the realistic in-memory pattern processing very inefficient and hard to scale-up.

To address these issues, we propose Sunder [67], a simple, compact, reconfigurable, and easy-to-implement reporting architecture by re-purpusing SRAM subarrays. Sunder leverages from Impala work, and processes reconfigure number of nibbles (4-bit symbols) in parallel instead of one 8-bit symbol. The key insight of our work is that transforming 8-bit processing to 4-bit processing reduces hardware resources for state-matching exponentially and introduces higher resource utilization. This, in turn, brings the opportunity to have a denser design and be able to utilize memory for reporting data.

Sunder introduces localized report buffers distributed across the chip close to where data (i.e., report states) are located. This approach helps Sunder to share many of the report buffer peripherals with the matching stage, and thus, incurring a negligible hardware overhead (less than 2%). In addition, our solution provides a simple mechanism to easily summarize the reporting data, and selectively read only the portion of the data that the application requires at run-time. We hope that our complete solution for in-memory pattern processing helps to realize its adoption in the industry.

#### 1.1.5 Summary

This dissertation work focuses on developing memory-centric hardware accelerators and the associated software stack to accelerate complex pattern recognition/processing [1, 2, 56, 4, 66, 68, 27, 4, 69, 66, 70, 56, 39], the combination of which forms a hardware/software co-design that enables high-performance and energy-efficient complex pattern processing.

We present an open-source automata processing simulator and a compiler that simulates, minimizes, compresses, and transforms a set of automata to different symbol sizes, and efficiently maps them to the hardware resources in memory-centric architectures, such as FPGAs, Cache Automaton [30], eAP [4], etc. We then present *Grapefruit*, the first open-source, full-stack, comprehensive, and scalable framework for automata processing on FPGAs. Grapefruit provides an extensive set of compiler optimizations, hardware optimizations, and design parameters for design-space exploration on a wide range of emerging applications. We then introduce Impala, a software/hardware methodology for multi-stride in-memory automata processing by repurposing SRAM subarrays. Impala proposes three-fold area, throughput, and energy benefits at the expense of increased offline compilation time. We finally present Sunder, a simple, compact, reconfigurable, and easy-to-implement reporting architecture for memory-centric pattern matching solutions.

This set of works provide solutions to enable performance, power, and area improvements in memory-centric pattern matching accelerators over prior work, which confirms our hypothesis.

#### 1.2 Overview of Dissertation

The remainder of this dissertation is organized as follows:

Chapter 2: Background introduces automata processing, discusses automata-related theory, prior approaches and architectures for automata processing.

Chapter 3: Automata Simulation and Transformation presents an open-source automata processing simulator and a compiler that simulates, minimizes, compresses, and transforms automata.

Chapter 4: Multi-Symbol Processing on FPGAs presents the first open-source, full-stack, comprehensive, and scalable framework for automata processing on FPGAs.

Chapter 5: Algorithm/Architecture Methodology for In-Memory Multi-Stride Pattern Matching introduces a software/hardware methodology for multi-stride in-memory automata processing by re-purposing SRAM subarrays.

8

Chapter 6: Enabling Low-Overhead Reporting Architecture in Memory-Centric Pattern Matching Accelerators presents a simple, compact, reconfigurable, and easy-to-implement reporting architecture for memory-centric pattern matching solutions.

Chapter 7: Conclusions summarizes the dissertation and discusses the implications of this work and potential future directions of research.

### Chapter 2

# Background

#### 2.1 Finite Automata

A finite automaton (FA) is a finite state machine (FSM) that accepts or rejects strings of symbols.

An FA is a mathematical model of computing and is represented by a 5-tuple,  $(Q, \Sigma, \Delta, q_0, F)$ , where Q is a finite set of states,  $\Sigma$  is a finite set of symbols,  $\Delta$  is a transition function,  $q_0$  are initial states, and F is a set of final or accepting states. An automaton has one or more start states that initiate computation, and one or more accept states that report a match. The transition function determines the next states using the current active states and the input symbol just read. If an input symbol causes the automata to enter into an accept state, the current position of the input symbol is reported.

A deterministic finite automaton (DFA) allows only one transition per input symbol. A non-deterministic finite automaton (NFA) has the ability to be in several states at once, meaning that transitions from a state on an input symbol can be to any set of states. DFAs and NFAs have equal computational power and can be converted to each other. However, a DFA can have exponentially more states that an equivalent NFA, which greatly increases the memory footprint. On the other hand, an NFA can have many parallel transitions, which is bounded by the limited memory bandwidth in von-neumann architectures.

#### 2.2 Automata Processing on von Neumann Architectures

On CPUs, NFAs and DFAs are represented by tables indicating each state's successor state(s) upon a rule match. DFAs are often the basis for implementing automata on CPUs because they have predictable memory bandwidth requirements; while an NFA may have many active states and may require many state lookups to process a single input symbol (potentially leading to a very large memory bandwidth requirement), a DFA requires just one. On the other hand, DFA tables are often too large to fit in the processor caches, because DFAs often suffer an exponential increase in the number of states relative to NFAs.

There are several efforts for high-speed regex processing on the CPUs and GPUs [71, 72, 73]. iNFAnt [73] is a parallel engine for regular expressions on GPUs with the support for multi-striding (processing multiple input bytes in each step). Graphics processing units (GPUs) provide a large number of parallel resources, which can help in hiding the DRAM access latency. However, highly-random access patterns in automata processing exhibit poor memory locality and increase branch divergence and need for synchronization [44].

Generally, automata processing on von Neumann architectures exhibits highly irregular memory access patterns with poor temporal and spatial locality, which often leads to poor cache and memory behavior [44]. Therefore, even high-throughput off-the-shelf von Neumann architectures struggle to meet today's big-data and streaming line-rate pattern processing requirements.

#### 2.3 Automata Processing on Memory-Centric Architectures

To cope with the memory wall problem in conventional von Neumann architectures, in-memory automata processing hardware accelerators have been proposed and have shown several orders of magnitude speedup compared to CPUs and GPUs [74].